Most of the slides in this lecture are either from or adapted from slides provided by the authors of the textbook "Computer Systems: A Programmer's Perspective," 2<sup>nd</sup> Edition and are provided from the website of Carnegie-Mellon University, course 15-213, taught by Randy Bryant and David O'Hallaron in Fall 2010. These slides are indicated "Supplied by CMU" in the notes section of the slides.

This is the first of two lectures on memory hierarchy. The second, covering secondary storage (disk, etc.) will be given in a few weeks.

### **Random-Access Memory (RAM)** · Key features - RAM is traditionally packaged as a chip - basic storage unit is normally a cell (one bit per cell) - multiple RAM chips form a memory Static RAM (SRAM) - each cell stores a bit with a four- or six-transistor circuit - retains value indefinitely, as long as it is kept powered - relatively insensitive to electrical noise (EMI), radiation, etc. - faster and more expensive than DRAM Dynamic RAM (DRAM) - each cell stores bit with a capacitor; transistor is used for access - value must be refreshed every 10-100 ms - more sensitive to disturbances (EMI, radiation,...) than SRAM - slower and cheaper than SRAM CS33 Intro to Computer Systems XVII–2

## SRAM vs DRAM Summary

|      | Trans.<br>per bit | Access<br>time | Needs<br>refresh? | Needs<br>EDC? | Cost | Applications                    |

|------|-------------------|----------------|-------------------|---------------|------|---------------------------------|

| SRAM | 4 or 6            | 1X             | No                | Maybe         | 100x | Cache memories                  |

| DRAM | 1                 | 10X            | Yes               | Yes           | 1X   | Main memories,<br>frame buffers |

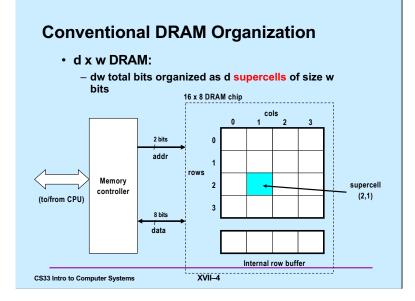

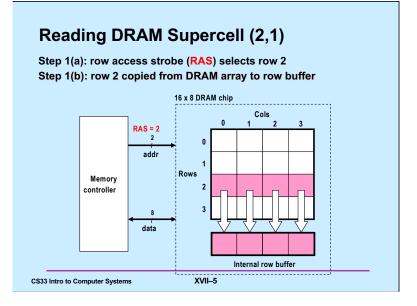

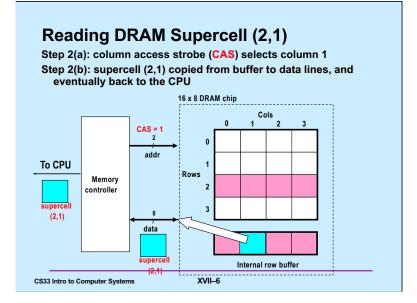

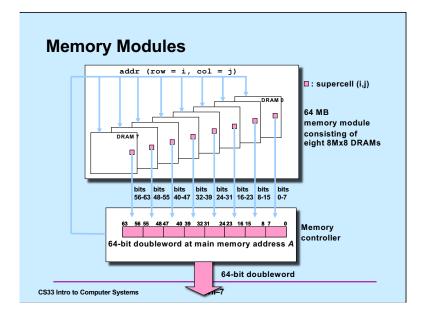

Note that the chip in the slide contains 16 supercells of 8 bits each. The supercells are organized as a 4x4 array.

The memory controller pulls in eight supercells from eight DRAM modules and transfers them to the processor over the memory bus.

Adapted from a slide supplied by CMU.

This slide is based on figures from **What Every Programmer Should Know About Memory** (http://www.akkadia.org/drepper/cpumemory.pdf), by Ulrich Drepper. It's an excellent article on memory and caching.

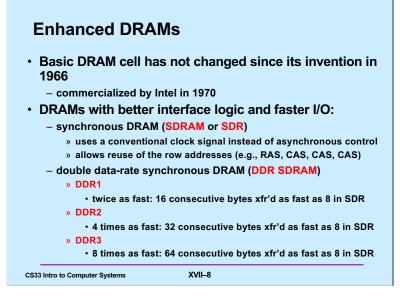

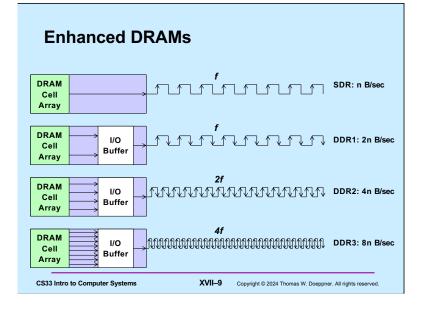

It is costly to make DRAM cell arrays run at a faster rate. Thus, rather than speed up the operation of the individual modules, they are organized to transfer in parallel. Thus, all that needs to be sped up is the bus that carries the data (something that is relatively inexpensive to do).

With SDR (Single Data-Rate DRAM), the DRAM cell array produces data at the same frequency as the memory bus, sending data on the rising edge of the signal.

With DDR1 (double data-rate), data is sent twice as fast by "double-pumping" the bus: sending data on both the rising and falling edges of the signal. To get data out of the cell array at this speed, data from two adjacent supercells are produced at once. These are buffered so that one doubleword at a time can be transmitted over the bus.

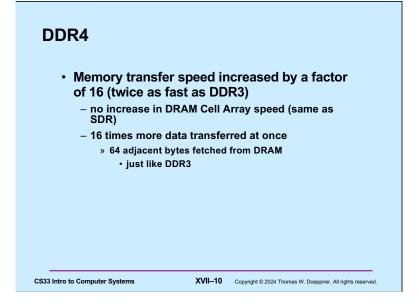

With DDR2, the frequency of the memory bus is doubled, and four supercells are produced at once. DDR3 takes this one step further, with eight supercells being produced at once. DDR4 takes this a step further and delivers 16 supercells at once.

Note that the processor fetches and stores 64 bytes of data at a time (for reasons having to do with caching, which we cover later in this lecture).

DDR4 memory became available in 2015. It's 16 times as fast as SDRAM, but transfers 64 consecutive bytes at a time, the same as DDR3. DDR5 is currently being discussed.

## Quiz 2

A program is loading randomly selected bytes from memory. These bytes will be delivered to the processor on a DDR4 system at a speed that's n times that of an SDR system, where n is:

a) 8

b) 4 c) 2

d) 1

u) i

CS33 Intro to Computer Systems

XVII-11 Copyright © 2024 Thomas W. Doeppner. All rights reserved.

## A Mismatch

- A processor clock cycle is ~0.3 nsecs

- Older SunLab machines (Intel Core i5-4690) run at 3.5 GHz

- Basic operations take 1 10 clock cycles – .3 – 3 nsecs

- Accessing memory takes 70-100 nsecs

- How is this made to work?

#### CS33 Intro to Computer Systems

XVII-12 Copyright © 2024 Thomas W. Doeppner. All rights reserved.

| Caching to the                 | e Rescue |                                                           |

|--------------------------------|----------|-----------------------------------------------------------|

|                                | CPU      |                                                           |

|                                | Cache    |                                                           |

|                                | R        |                                                           |

| CS33 Intro to Computer Systems | XVII–13  | Copyright © 2024 Thomas W. Doeppner, All rights reserved. |

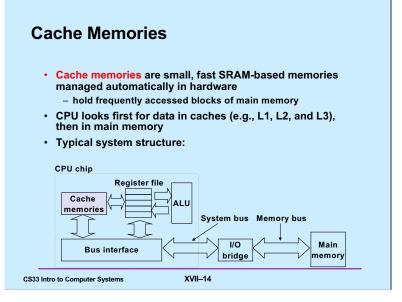

Sitting between the processor and RAM are one or more caches. (They actually are on the chip along with the processor.) Recently accessed items by the processor reside in the cache, where they are much more quickly accessed than directly from memory. The processor does a certain amount of pre-fetching to get things from RAM before they are needed. This involves a certain amount of guesswork, but works reasonably well, given well behaved programs.

"ALU" (arithmetic and logic unit) is a traditional term for the instruction and execution units of a processor.

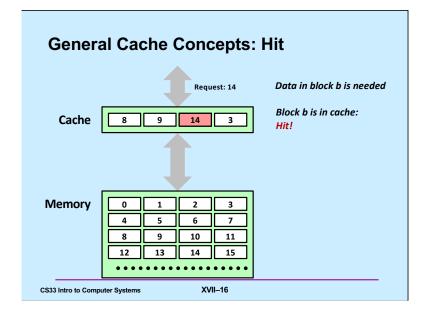

#### **General Cache Concepts** Smaller, faster, more expensive Cache memory caches a subset of the blocks Data is copied in block-sized transfer units Larger, slower, cheaper memory viewed as partitioned into "blocks" Memory ..... XVII–15 CS33 Intro to Computer Systems

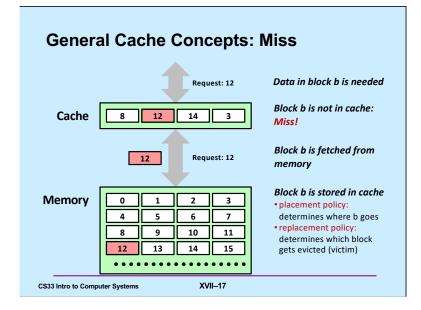

# General Caching Concepts: Types of Cache Misses • Cold (compulsory) miss – cold misses occur because the cache is empty

- Conflict miss

- most caches limit blocks to a small subset (sometimes a singleton) of the block positions in RAM

- » e.g., block i in RAM must be placed in block (i mod 4) in the cache

- conflict misses occur when the cache is large enough, but multiple data objects all map to the same cache block

» e.g., referencing blocks 0, 8, 0, 8, 0, 8, ... would miss every time

- Capacity miss

- occurs when the set of active cache blocks (working set) is larger than the cache

XVII–18

CS33 Intro to Computer Systems

| Direct-Mapped                  | d Ca                                                              | ach  | e Simula                      | ation |

|--------------------------------|-------------------------------------------------------------------|------|-------------------------------|-------|

|                                | M=16 byte addresses, B=2 bytes/block,<br>S=4 sets, E=1 Blocks/set |      |                               |       |

|                                | Address trace (reads, one byte per read):                         |      |                               |       |

|                                |                                                                   | 0    | [0000 <sub>2</sub> ],         | miss  |

|                                |                                                                   | 1    | [0001 <sub>2</sub> ],         | hit   |

|                                |                                                                   | 7    | [0111 <sub>2</sub> ],         | miss  |

|                                |                                                                   | 8    | [1000₂],                      | miss  |

|                                |                                                                   | 0    | [0 <u>00</u> 0 <sub>2</sub> ] | miss  |

|                                | v                                                                 | Tag  | Block                         |       |

| Set 0                          | 1                                                                 | 0    | M[0-1]                        |       |

| Set 1                          |                                                                   |      |                               |       |

| Set 2                          |                                                                   |      |                               |       |

| Set 3                          | 1                                                                 | 0    | M[6-7]                        |       |

| CS33 Intro to Computer Systems |                                                                   | XVII | -21                           |       |

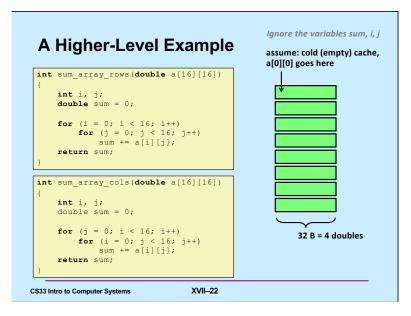

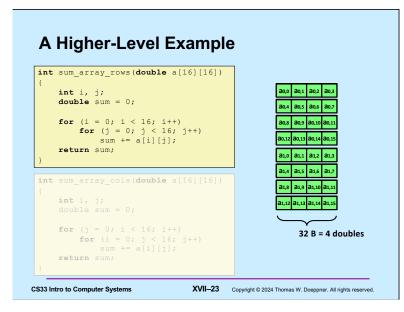

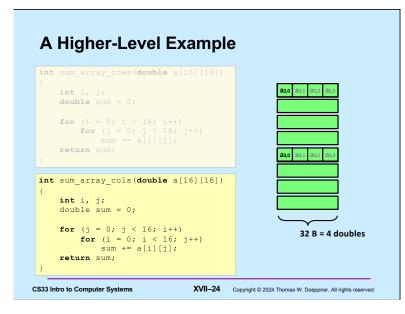

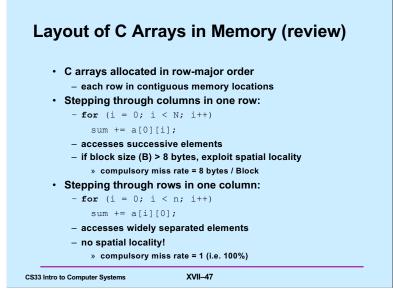

Note that the cache holds two rows of the matrix; each cache block holds four doubles. When a[0][0] is read, so are a[0][1] through a[0][3]. Thus, after one cache miss, we get three hits.

For each reference to an element of the matrix, its entire row is brought into the cache, even though the rest of the row is not immediately used.

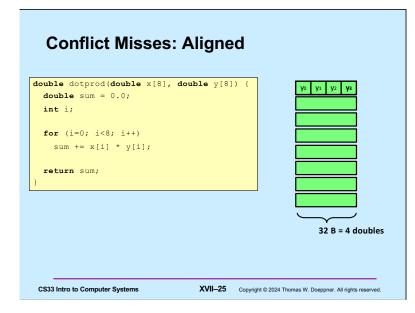

If arrays x and y have the same alignment, i.e., both start in the same cache set, then each access to an element of y replaces the cache line containing the corresponding element of x, and vice versa. The result is that the loop is executed very slowly — each access to either array results in a conflict miss.

| -                      | double x[8], do | <b>uble</b> y[8]) { | xo         | X1 X2 X3        |

|------------------------|-----------------|---------------------|------------|-----------------|

| double sum = (         | 0.0;            |                     | X4         | X5 X6 X7        |

| <pre>int i;</pre>      |                 |                     | <b>y</b> 4 | ys y6 y7        |

| for (i=0; i<8)         | : i++)          |                     |            |                 |

| sum += x[i]            | * y[i];         |                     |            |                 |

|                        |                 |                     |            |                 |

| <pre>return sum;</pre> |                 |                     |            |                 |

|                        |                 |                     |            |                 |

|                        |                 |                     |            |                 |

|                        |                 |                     |            | 32 B = 4 double |

|                        |                 |                     |            | 32 B = 4 double |

However, if the two arrays start in different cache sets, then the loop executes quickly — there is a cache miss on just every fourth access to each array.

Many of the slides in this lecture are either from or adapted from slides provided by the authors of the textbook "Computer Systems: A Programmer's Perspective," 2<sup>nd</sup> Edition and are provided from the website of Carnegie-Mellon University, course 15-213, taught by Randy Bryant and David O'Hallaron in Fall 2010. These slides are indicated "Supplied by CMU" in the notes section of the slides.

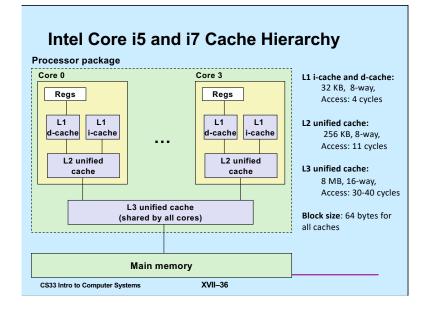

The L3 cache is known as the last-level cache (LLC) in the Intel documentation.

One concern is whether what's contained in, say, the L1 cache is also contained in the L2 cache. if so, caching is said to be **inclusive**. If what's contained in the L1 cache is definitely not contained in the L2 cache, caching is said to be **exclusive**. An advantage of exclusive caches is that the total cache capacity is the sum of the sizes of each of the levels, whereas for inclusive caches, the total capacity is just that of the largest. An advantage of inclusive caches is that what's been brought into the cache hierarchy by one core is available to the other cores.

AMD processors tend to have exclusive caches; Intel processors tend to have inclusive caches.

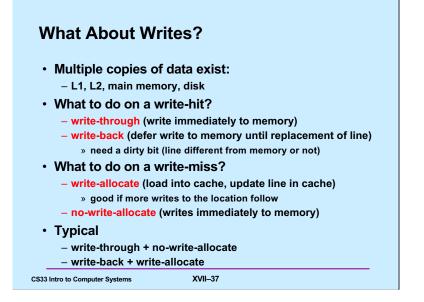

Most current processors use the write-back/write-allocate approach. This causes some (surmountable) difficulties for multi-core processors that have a separate cache for each core.

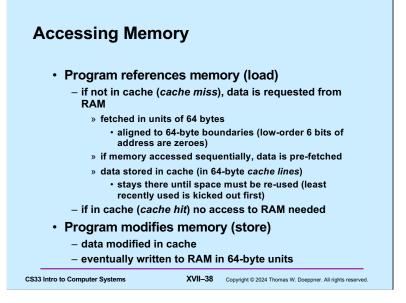

This slide describes accessing memory on Intel Core I5 and I7 processors.

If the processor determines that a program is accessing memory sequentially (because the past few accesses have been sequential), then it begins the load of the next block from memory before it is requested. If this determination was correct, then the memory will be in the cache (or well on its way) before it's needed.

| Locality                                                      |                                                                                    |

|---------------------------------------------------------------|------------------------------------------------------------------------------------|

| data and instruct                                             | lity: programs tend to use<br>ions with addresses near or<br>ey have used recently |

| Temporal locality                                             |                                                                                    |

| <ul> <li>recently reference<br/>to be referenced a</li> </ul> | ed items are likely<br>again in the near future                                    |

| Spatial locality:                                             |                                                                                    |

| <ul> <li>items with nearby<br/>to be referenced of</li> </ul> | / addresses tend<br>close together in time                                         |

|                                                               |                                                                                    |

| CS33 Intro to Computer Systems                                | XVII–41                                                                            |

| Locality Exa                                                  | mple                                                                             |                                       |

|---------------------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------------|

|                                                               | <pre>sum = 0;<br/>for (i = 0; i &lt; n; i<br/>sum += a[i];<br/>return sum;</pre> | ++)                                   |

| pattern)                                                      |                                                                                  | Spatial locality<br>Temporal locality |

| Instruction refe     – reference instru     – cycle through I | uctions in sequence.                                                             | Spatial locality<br>Temporal locality |

| CS33 Intro to Computer Systems                                | XVII–42                                                                          |                                       |

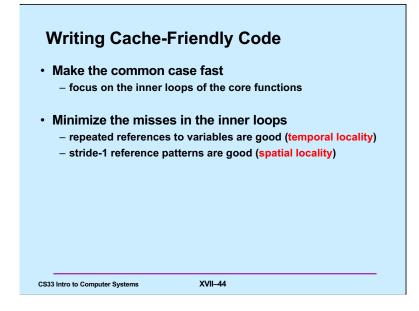

"Stride n" reference patterns are sequences of memory accesses in which every nth element is accessed in memory order. Thus stride 1 means that every element is accessed, starting at the beginning of a memory area, continuing to its end.

Based on slides supplied by CMU.

Adapted form a slide by CMU.

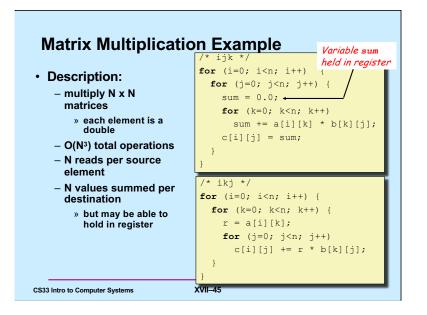

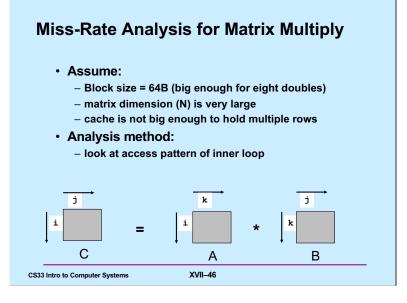

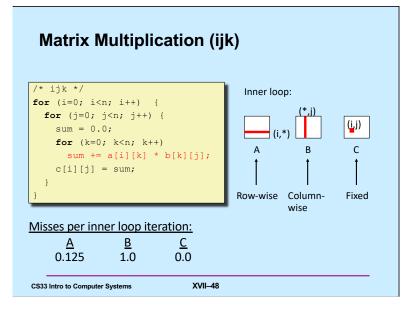

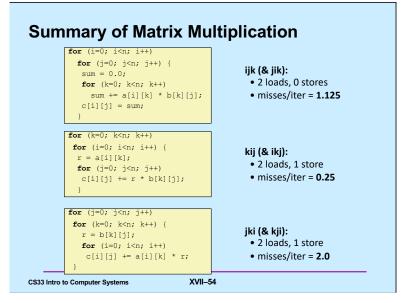

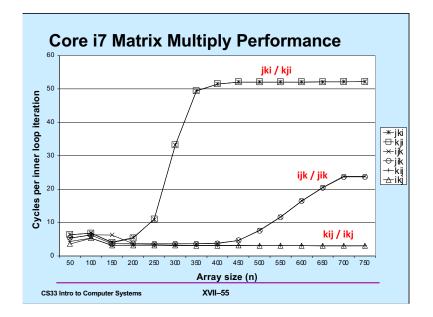

Assume we are multiplying arrays of doubles, thus each element is eight bytes long, and thus a cache line holds eight matrix elements. The slide shows a straightforward implementation of multiplying A and B to produce C.

### Matrix Multiplication (jik) /\* jik \*/ Inner loop: for (j=0; j<n; j++) {</pre> for (i=0; i<n; i++) {</pre> (\*,j) (<mark>i</mark>j) sum = 0.0;(i,\* for (k=0; k<n; k++)</pre> В А С sum += a[i][k] \* b[k][j]; c[i][j] = sum} Row-wise Column-Fixed wise Misses per inner loop iteration: <u>C</u> 0.0 B <u>A</u> 0.125 1.0 XVII–49 CS33 Intro to Computer Systems

Supplied by CMU.

If we reverse the order of the two outer loops, there's no change in results or performance.

### Matrix Multiplication (kij) /\* kij \*/ Inner loop: for (k=0; k<n; k++) {</pre> (i,k) for (i=0; i<n; i++) {</pre> (k,\*) (i,\*) r = a[i][k]; **for** (j=0; j<n; j++) А В c[i][j] += r \* b[k][j]; } Row-wise Row-wise Fixed Misses per inner loop iteration: <u>A</u> 0.0 <u>C</u> B 0.125 0.125 XVII–50 CS33 Intro to Computer Systems

Supplied by CMU.

Moving the loop on k to be the outer loop does not affect the result, but it improves performance.

###

| <pre>for (j=0; j<n; *="" +="r" b[k][="" c[i][j]="" j++)="" pre="" }<=""></n;></pre> | j]; ↑<br>Fixed                | B<br>T<br>Row-wise | C<br>T<br>Row-wise |

|-------------------------------------------------------------------------------------|-------------------------------|--------------------|--------------------|

| <u>Misses per inner loop iteration</u><br><u>A</u> <u>B</u><br>0.000.1250.          | <u>on:</u><br><u>C</u><br>125 |                    |                    |

|                                                                                     |                               |                    |                    |

(k,\*)

(i,\*)

Supplied by CMU.

Switching the two outer loops affects neither results nor performance.

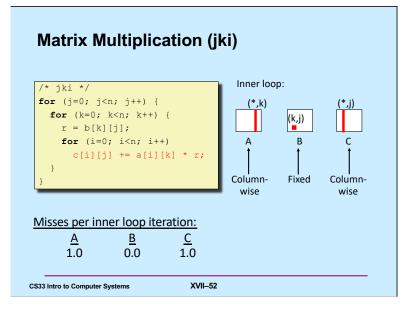

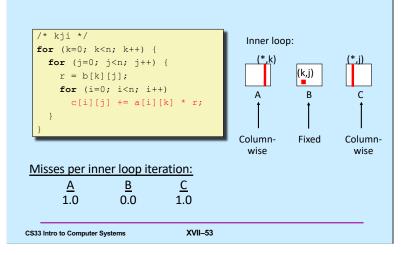

Moving the loop on i to be the inner loop makes performance considerably worse.

## Matrix Multiplication (kji)

Supplied by CMU.

The poor performance is not improved by reversing the outer loops.

| In Real Life                                                                                                    |

|-----------------------------------------------------------------------------------------------------------------|

| <ul> <li>Multiply two 1024x1024 matrices of doubles<br/>on core i5 machines (formerly in the Sunlab)</li> </ul> |

| − ijk<br>» 4.185 seconds                                                                                        |

| − kij<br>» 0.798 seconds                                                                                        |

| −jki<br>» 11.488 seconds                                                                                        |

| CS33 Intro to Computer Systems XVII–56 Copyright © 2024 Thomas W. Doeppner. All rights reserved.                |

| Architectural Support for the OS                                                                 |

|--------------------------------------------------------------------------------------------------|

| Not all instructions are created equal                                                           |

| <ul> <li>non-privileged instructions</li> </ul>                                                  |

| » can affect only current program                                                                |

| <ul> <li>privileged instructions</li> </ul>                                                      |

| » may affect entire system                                                                       |

| Processor mode                                                                                   |

| – user mode                                                                                      |

| » can execute only non-privileged instructions                                                   |

| <ul> <li>privileged mode</li> </ul>                                                              |

| » can execute all instructions                                                                   |

|                                                                                                  |

| CS33 Intro to Computer Systems XVII–63 Copyright © 2024 Thomas W. Doeppner. All rights reserved. |

## Which Instructions Should Be Privileged?

- I/O instructions

- Those that affect how memory is mapped

- Halt instruction

- Some others ...

CS33 Intro to Computer Systems

XVII-64 Copyright © 2024 Thomas W. Doeppner. All rights reserved.

## Who Is Privileged?

- No one

- user code always runs in user mode

- The operating-system kernel runs in privileged mode

- nothing else does

- not even super user on Unix or administrator on Windows

CS33 Intro to Computer Systems

XVII-65 Copyright © 2024 Thomas W. Doeppner. All rights reserved.

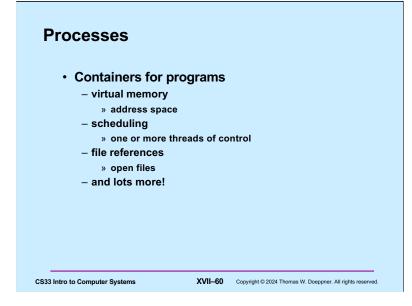

## <section-header><section-header><section-header><section-header><section-header><section-header><section-header><list-item><list-item><list-item><list-item>

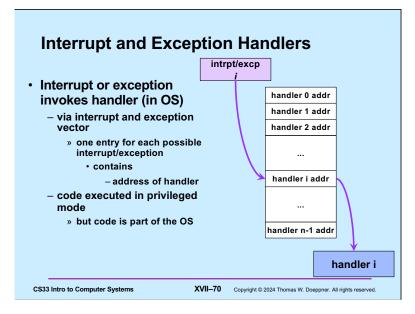

### Interrupts and Exceptions

- Things don't always go smoothly ...

- I/O devices demand attention

- timers expire

- programs demand OS services

- programs demand storage be made accessible

- programs have problems

- Interrupts

- demand for attention from external sources

- Exceptions

- executing program requires attention

CS33 Intro to Computer Systems

XVII-67 Copyright © 2024 Thomas W. Doeppner. All rights reserved.

# <section-header><section-header><section-header><section-header><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><section-header>

These definitions follow those given in "Intel® 64 and IA-32 Architectures Software Developer's Manual" and are generally accepted even outside of Intel.

| Actions for Interrupts and Exceptions                                                            |

|--------------------------------------------------------------------------------------------------|

| When interrupt or exception occurs                                                               |

| <ul> <li>processor saves state of current thread/process on<br/>stack</li> </ul>                 |

| <ul> <li>processor switches to privileged mode (if not<br/>already there)</li> </ul>             |

| <ul> <li>invokes handler for interrupt/exception</li> </ul>                                      |

| <ul> <li>if thread/process is to be resumed (typical action<br/>after interrupt)</li> </ul>      |

| » thread/process state is restored from stack                                                    |

| <ul> <li>if thread/process is to re-execute current<br/>instruction</li> </ul>                   |

| » thread/process state is restored, after backing up<br>instruction pointer                      |

| <ul> <li>if thread/process is to terminate</li> </ul>                                            |

| » it's terminated                                                                                |

| CS33 Intro to Computer Systems XVII–69 Copyright © 2024 Thomas W. Doeppner. All rights reserved. |

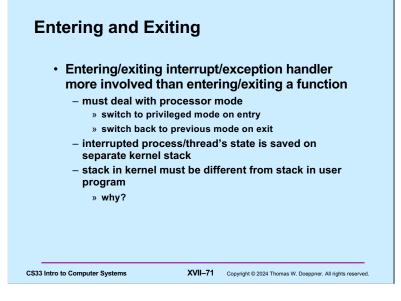

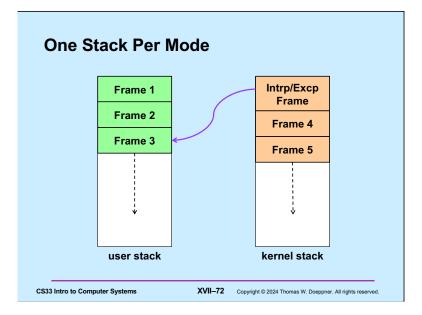

The reason why there must be a separate stack in privileged mode is that the OS must be guaranteed that when it is executing, it has a valid stack, and that the stack pointer must be pointing to a region of memory that can be used as a stack by the OS. Since while the program was running in user mode any value could have been put into the stack-pointer register, when the OS is invoked, it switches to a pre-allocated stack set up just for it.

When a trap or interrupt occurs, the current processor state (registers, including RIP, condition codes, etc.) are saved on the kernel stack. When the system returns back to the interrupted program, this state is restored.

## Quiz 3

If an interrupt occurs, which general-purpose registers must be pushed onto the kernel stack?

a) all

b) none

CS33 Intro to Computer Systems

c) callee-save registers

d) caller-save registers

XVII-73 Copyright © 2024 Thomas W. Doeppner. All rights reserved.